AD9531BCPZ เครื่องกําเนิดนาฬิกา 1.6GHz Output Jitter andlt;1ps 3.3V/5V Supply SPI Control LVDS/PECL Outputs Industrial Temp สําหรับ 5G/ไร้สาย/เครือข่าย

และnbsp

และ FECTS

3 พื้นที่ PLL / VCO ที่บูรณาการอย่างเต็มที่ (PLL1, PLL2, และ PLL3)

และ PLL1, โหมด N ส่วน, ความกว้างแบนด์ 12 kHz ถึง 20 MHz

การสูญเสียค่าพิจารณาและการตรวจพบล็อคสําหรับ PLL แต่ละลํา

การแปลงความถี่ทั่วไปที่สามารถตั้งค่าด้วยปิน

อัตโนมัติการร่วมกันของผลิตทั้งหมดบนพลังงานขึ้น

ความสามารถในการปรับ synchronization output ด้วยมือ

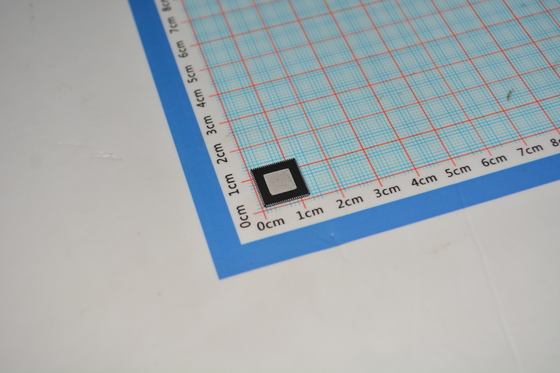

แพ็คเกจมีใน LFCSP 88 หลัก

รายละเอียด PLL1

และ และ โหมด N/N

และnbsp; VCXOภายนอกเป็นตัวเลือก

และnbsp; รูปแบบการชะลอคงที่สําหรับการสับเปลี่ยนเฟสสแตตติกคงที่

และnbsp; 2 การเข้าของนาฬิกาอ้างอิง

และnbsp; และnbsp; และnbsp;รูปแบบการใส่: ความแตกต่าง / สิ้นเดียว

ระยะความถี่: 9.5 MHz ถึง 260 MHz

และ และ การสลับมาตรฐาน: มือ / อัตโนมัติ

และ 10 การออก HSTL/CMOS ความดันต่ําสุดถึง 400 MHz รายละเอียด PLL2

และ โหมดอินเทเจอร์-N (หน่วยเข้านาฬิกามาตรฐาน)

และnbsp; และnbsp; และnbsp;รูปแบบการใส่: อนุพันธ์/ปลายเดียว/คริสตัล1

ระยะความถี่: 9.5 MHz ถึง 250 MHz

และ 12 HSTL/CMOS ออกถึง 400 MHz

รายละเอียด PLL3

และ โหมดอินเทเจอร์-N (หน่วยเข้านาฬิกามาตรฐาน)

และ และ รูปแบบการใส่: อนุพันธ์/ปลายเดียว/คริสตัล1

ระยะความถี่: 9.5 MHz ถึง 250 MHz

และnbsp; 12 HSTL / CMOS ออกสูงสุด 400 MHz

รายละเอียด PLL3

และ โหมดอินเทเจอร์-N (หน่วยเข้านาฬิกามาตรฐาน)

ระยะความถี่: 9.5 MHz ถึง 100 MHz

รูปแบบการเข้า: ความแตกต่าง / คริสตัล (สนับสนุน 25 MHz ถึง

และ และ 50 MHz AT-cut quartz crystal resonator)

และnbsp; 2 HSTL/LVDS/CMOS ออกที่ 400 MHz/150 MHz (ความแตกต่าง/CMOS)

และnbsp

การใช้งาน

การกําหนดเวลาของเครื่องควบคุมเครื่องวิทยุ

การผลิตและการกระจายนาฬิกาที่มีความรุนแรงต่ํา/เสียงเสียงระยะ

การผลิตและแปลนาฬิกาสําหรับ SONET, 10GE, 10G FC และโปรโตคอล 10 Gbps อื่นๆ

การ์ดสายเครือข่าย 40 Gbps/100 Gbps รวมถึง SONET, Ethernet สมอง, OTU2/3/4

การแก้ไขความผิดพลาดในอนาคต (G.710)

เครื่องรับสัญญาณไร้สายที่มีประสิทธิภาพสูง

ATE และเครื่องมือที่มีประสิทธิภาพสูง

โครงสร้างพื้นฐานเบนด์กว้าง

การ์ดสาย Ethernet, สวิตช์และรูเตอร์

SATA และ PCI-express

และnbsp

คําอธิบาย

AD9531 ให้ฟังก์ชันเครื่องกําเนิดนาฬิกาหลายอัตราออก และสามเนื้อหาในชิปแบบล็อคเฟส (PLL) ด้วยความถี่และรูปแบบการออกที่สามารถโปรแกรมได้ด้วย SPI

PLL1 ให้ข้อมูลเข้า 2 ตัวและ 10 ตัว และรวมถึงการตั้งค่าวงจรที่ผู้ใช้สามารถเลือกได้ 4 ตัวPLL มีกรองวงจรที่บูรณาการอย่างสมบูรณ์แบบที่ต้องการเพียงตัวประกอบภายนอกเดียว (หรือเครือข่าย RC ซีรี). PLL1 ให้ความถี่ออกแบบที่กว้างขวางถึง 400 MHz และสามารถทํางานกับเครื่องหมุนกระจกระจกระจกระจกระจกระจกระจกระจกระจกระจกระจกระจก (VCXO) และฟิลเตอร์วงจรแทนเครื่องหมั่นที่ควบคุมความกระชับกําลัง (VCO) และกรองวงจร.

PLL2 เป็น PLLจํานวนเต็ม-N ที่ให้ข้อมูลเข้าระดมเดียวและ 12 ผลิตPLL2 สัมผัสความถี่การออกสูงสุด 400 MHz จากแหล่ง REF2_x และปรับ synchronizes นาฬิกาการออกไปยังข้อมูลการเข้า.

PLL3 ให้การเข้าอัตราการอ้างอิงเดียวและการออกอัตราการออกอัตราการออกอัตราการออกสูงสุด 400 MHz จากแหล่ง REF3_x และทําให้นาฬิกาการออกอัตราการเข้าอัตราการเข้าAD9531 มีใน LFCSP 88 สายด่วนและถูกระบุมากกว่าและลบระยะอุณหภูมิการทํางาน 40 °C ถึง + 85 °C

ทั่วใบข้อมูลนี้ ปินหลายฟังก์ชัน เช่น LOR/M4 จะถูกระบุด้วยชื่อปินทั้งหมด หรือด้วยฟังก์ชันเดียวของปิน (เช่น LOR,เมื่อมีแต่ฟังก์ชันนั้นเท่านั้นที่สําคัญ)ในกรณีอื่น ๆ ข้อความและรูปภาพของใบข้อมูลนี้มีอ้างอิงไปยังช่องทางแทนปิน เช่น REF_A อ้างอิงไปยังช่องทาง REF_A แทนที่ REF_AP และ REF_AN pinเหมือนกัน, OUT3_1 หมายถึงช่อง 1 ของ PLL3 แทนที่ OUT3_1P และ OUT3_1N ปิน. นอกจากนี้, คําอักษรสั้นสําหรับคู่ปินแทนการอ้างอิงอย่างชัดเจนต่อปินแต่ละตัว (เช่น,REF_Ax หมายถึง REF_AN และ REF_AP pin.)

และnbsp

ข้อมูล

|

ประเภท

|

|

และnbsp

|

|

ผู้ผลิต

|

Analog Devices Inc. (บริษัทอุปกรณ์แอนาล็อก)

|

|

|

ซีรี่ย์

|

|

|

|

การบรรจุ

|

|

|

|

สถานะของส่วน

|

|

|

|

DigiKey สามารถเขียนโปรแกรมได้

|

|

|

|

PLL

|

|

|

|

หน่วยงาน

|

CMOS, LVDS, LVPECL, คริสตัล

|

|

|

ผลิต

|

|

|

|

จํานวนวงจร

|

|

|

|

อัตราส่วน - อินทุ้น:ผลิต

|

|

|

|

อัตราการแตกต่าง - Input:Output

|

|

|

|

ความถี่ - สูงสุด

|

|

|

|

ตัวแบ่ง/ตัวคูณ

|

|

|

|

โลเตจ - การให้บริการ

|

|

|

|

อุณหภูมิการทํางาน

|

|

|

|

ประเภทการติดตั้ง

|

|

|

|

กล่อง / กระเป๋า

|

88-VFQFN พื้นที่เปิดเผย, CSP

|

|

|

แพ็คเกจอุปกรณ์ของผู้จําหน่าย

|

|

|

|

เลขสินค้าพื้นฐาน

|

|

และnbsp

การวาด

และnbsp

ข้อดีของเรา:

- ผลิตภัณฑ์ที่มีคุณภาพสูง --- ของเรานําเสนอเป็น 100% ของใหม่และเดิม, ROHS

- ราคาที่สามารถแข่งขันได้ --- ช่องทางการซื้อที่ดี

- บริการมืออาชีพ --- การทดสอบคุณภาพที่เข้มงวดก่อนการจัดส่ง และบริการหลังการขายที่สมบูรณ์แบบหลังจากการซื้อ

- อุปกรณ์ที่เหมาะสม --- ด้วยการสนับสนุนของทีมงานการซื้อสินค้าของเราที่แข็งแรง

- การจัดส่งเร็ว --- เราจะส่งสินค้าภายใน 1-3 วันทําการหลังจากการชําระเงินยืนยัน

และnbsp

ให้แน่ใจว่าจะตอบสนองความต้องการของคุณ สําหรับทุกชนิดของส่วนประกอบ^_^

รายการสินค้า

จําหน่ายชุดส่วนประกอบอิเล็กทรอนิกส์ ครบวงจร semiconductors ส่วนประกอบที่ทํางานและอัมพวา

ข้อเสนอต่างๆ ได้แก่

วงจรบูรณาการ IC ความจํา ไดโอเดส ทรานซิสเตอร์ คอนเดสซิเตอร์ ริสติสเตอร์ วาริสเตอร์ ฟิวส์ ทริมเมอร์ แอนด์แอมเปอร์ โปเทนติโอเมตร ทรานฟอร์เมอร์ แบตเตอรี่ เคเบิล รีเล่ย์ สวิตช์ คอนเนคเตอร์ เทอร์มินัล บล็อกคริสตัลแอนด์แอมเปอร์; ออสซิลเลอเตอร์ อินดูเตอร์ เซนเซอร์ ทรานฟอร์เมอร์ ไดรเวอร์ IGBT LED LCD เครื่องแปลง PCB PCB

แรงในแบรนด์:

ไมโครชิป MAX, AD, TI, ATMEL, ST, ON, NS, Intersil, Winbond, Vishay, ISSI, Infineon, NEC, FAIRCHILD, OMRON, YAGEO, TDK เป็นต้น

ข้อความของคุณจะต้องอยู่ระหว่าง 20-3,000 ตัวอักษร!

ข้อความของคุณจะต้องอยู่ระหว่าง 20-3,000 ตัวอักษร! กรุณาตรวจสอบอีเมลของคุณ!

กรุณาตรวจสอบอีเมลของคุณ!  ข้อความของคุณจะต้องอยู่ระหว่าง 20-3,000 ตัวอักษร!

ข้อความของคุณจะต้องอยู่ระหว่าง 20-3,000 ตัวอักษร! กรุณาตรวจสอบอีเมลของคุณ!

กรุณาตรวจสอบอีเมลของคุณ!